INSTITUTO FEDERAL SUL-RIO-GRANDENSE UNIVERSIDADE ABERTA DO BRASIL

Programa de Fomento ao Uso das TECNOLOGIAS DE COMUNICAÇÃO E INFORMAÇÃO NOS CURSOS DE GRADUAÇÃO - TICS

# Arquitetura e organização de computadores

**Lisandro Lemos Machado**

TICs

Ministério da **Educação**

### Copyright© 2011 Universidade Aberta do Brasil Instituto Federal Sul-rio-grandense

Apostila de Arquitetura e Organização de Computadores MACHADO, Lisandro Lemos.

2011/2

Produzido pela Equipe de Produção de Material Didático da Universidade Aberta do Brasil do Instituto Federal Sul-rio-grandense TODOS OS DIREITOS RESERVADOS

### **INSTITUTO FEDERAL SUL-RIO-GRANDENSE**

#### **UNIVERSIDADE ABERTA DO BRASIL**

Programa de Fomento ao Uso das TECNOLOGIAS DE COMUNICAÇÃO E INFORMAÇÃO NOS CURSOS DE GRADUAÇÃO - TICS

#### PRESIDÊNCIA DA REPÚBLICA

#### Dilma Rousseff

PRESIDENTE DA REPÚBLICA FEDERATIVA DO BRASIL

### MINISTÉRIO DA EDUCAÇÃO

#### Fernando Haddad

MINISTRO DO ESTADO DA EDUCAÇÃO

#### Luiz Cláudio Costa

SECRETÁRIO DE EDUCAÇÃO SUPERIOR - SESU

#### Eliezer Moreira Pacheco

SECRETÁRIO DA EDUCAÇÃO PROFISSIONAL E TECNOLÓGICA

### Luís Fernando Massonetto

SECRETÁRIO DA EDUCAÇÃO A DISTÂNCIA – SEED

#### Jorge Almeida Guimarães

PRESIDENTE DA COORDENAÇÃO DE APERFEIÇOAMENTO DE PESSOAL DE NÍVEL SUPERIOR - CAPES

### INSTITUTO FEDERAL DE EDUCAÇÃO, CIÊNCIA E TECNOLOGIA SUL-RIO-GRANDENSE [IFSUL]

#### Antônio Carlos Barum Brod

REITOR

### Daniel Espírito Santo Garcia

PRÓ-REITOR DE ADMINISTRAÇÃO E DE PLANEJAMENTO

#### Janete Otte

PRÓ-REITORA DE DESENVOLVIMENTO INSTITUCIONAL

### Odeli Zanchet

PRÓ-REITOR DE ENSINO

### Lúcio Almeida Hecktheuer

PRÓ-REITOR DE PESQUISA, INOVAÇÃO E PÓS-GRADUAÇÃO

### Renato Louzada Meireles

PRÓ-REITOR DE EXTENSÃO

### IF SUL-RIO-GRANDENSE CAMPUS PELOTAS

### José Carlos Pereira Nogueira

DIRETOR-GERAL DO CAMPUS PELOTAS

### Clóris Maria Freire Dorow

DIRETORA DE ENSINO

#### João Róger de Souza Sastre

DIRETOR DE ADMINISTRAÇÃO E PLANEJAMENTO

#### Rafael Blank Leitzke

DIRETOR DE PESQUISA E EXTENSÃO

### Roger Luiz Albernaz de Araújo

CHEFE DO DEPARTAMENTO DE ENSINO SUPERIOR

### IF SUL-RIO-GRANDENSE DEPARTAMENTO DE EDUCAÇÃO A DISTÂNCIA

#### Luis Otoni Meireles Ribeiro

CHEFE DO DEPARTAMENTO DE EDUCAÇÃO A DISTÂNCIA

#### Beatriz Helena Zanotta Nunes

COORDENADORA DA UNIVERSIDADE ABERTA DO BRASIL – LIAB/IESUL

#### Marla Cristina da Silva Sopeña

COORDENADORA ADJUNTA DA UNIVERSIDADE ABERTA DO BRASIL — UAB/ IFSUL

#### Cinara Ourique do Nascimento

COORDENADORA DA ESCOLA TÉCNICA ABERTA DO BRASIL – E-TEC/IFSUL

#### Ricardo Lemos Sainz

COORDENADOR ADJUNTO DA ESCOLA TÉCNICA ABERTA DO BRASIL – E-TEC/IFSUL

#### **IF SUL-RIO-GRANDENSE**

#### UNIVERSIDADE ABERTA DO BRASIL

#### Beatriz Helena Zanotta Nunes

COORDENADORA DA UNIVERSIDADE ABERTA DO BRASIL – UAB/IFSUL

#### Marla Cristina da Silva Sopeña

COORDENADORA ADJUNTA DA UNIVERSIDADE ABERTA DO BRASIL — UAB/ IFSUL

### Mauro Hallal dos Anjos

GESTOR DE PRODUÇÃO DE MATERIAL DIDÁTICO

### PROGRAMA DE FOMENTO AO USO DAS TECNOLOGIAS DE COMUNICAÇÃO E INFORMAÇÃO NOS CURSOS DE GRADUAÇÃO -TICs

#### Raquel Paiva Godinho

GESTORA DO EDITAL DE TECNOLOGIAS DE INFORMAÇÃO E COMUNICAÇÃO – TICS/IFSUL

#### Ana M. Lucena Cardoso

DESIGNER INSTRUCIONAL DO EDITAL TICS

### Lúcia Helena Gadret Rizzolo

REVISORA DO EDITAL TICS

Tics

### EQUIPE DE PRODUÇÃO DE MATERIAL DIDÁTICO - UAB/IFSUL

Lisiane Corrêa Gomes Silveira GESTORA DA EQUIPE DE DESIGN

Denise Zarnottz Knabach Felipe Rommel Helena Guimarães de Faria Lucas Quaresma Lopes EQUIPE DE DESIGN

Catiúcia Klug Schneider GESTORA DE PRODUÇÃO DE VÍDEO

Gladimir Pinto da Silva PRODUTOR DE ÁUDIO E VÍDEO

Marcus Freitas Neves EDITOR DE VÍDEO

João Eliézer Ribeiro Schaun GESTOR DO AMBIENTE VIRTUAL DE APRENDIZAGEM

Giovani Portelinha Maia GESTOR DE MANUTENÇÃO E SISTEMA DA INFORMAÇÃO

Carlo Camani Schneider Efrain Becker Bartz Jeferson de Oliveira Oliveira Mishell Ferreira Weber EQUIPE DE PROGRAMAÇÃO PARA WEB

## SUMÁRIO S

| UNIDADE A - CONCEITOS BÁSICOS   13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | GUIA DIDÁTICO                                    |      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------|

| Informação                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | UNIDADE A - CONCEITOS BÁSICOS                    | 13   |

| Clock       16         Transmissão de dados       11         Taxa de transferência       23         Arquitetura física de sistemas computacionais       21         UNIDADE B - UNIDADE CENTRAL DE PROCESSAMENTO       31         Execução de programas       33         Clock       34         Arquitetura do processador       36         Execução de instruções       39         Programação de processador       44         Processador hipotético       46         UNIDADE C - SISTEMA DE MEMÓRIA       61         Hierarquia de memórias       64         Memória RAM       66         Memória Cache       76         Memória secundária       82         UNIDADE D - DISPOSITIVOS DE ENTRADA E SAÍDA       93         Categoria de dispositivos de E/S       95         Endereços de I/O       97         Barramentos de E/S       96         DMA       96         UNIDADE E - TIPOS DE ORGANIZAÇÃO DE COMPUTADORES       101         Arquiteturas paralelas       102                                                                                                                                          |                                                  |      |

| Transmissão de dados         15           Taxa de transferência         21           Arquitetura física de sistemas computacionais         23           UNIDADE B - UNIDADE CENTRAL DE PROCESSAMENTO         31           Execução de programas         33           Clock         34           Arquitetura do processador         36           Execução de instruções         36           Programação de processador         44           Processador hipotético         44           UNIDADE C - SISTEMA DE MEMÓRIA         61           Hierarquia de memórias         66           Memória ROM         66           Memória Cache         76           Memória Secundária         82           UNIDADE D - DISPOSITIVOS DE ENTRADA E SAÍDA         93           Categoria de dispositivos de E/S         95           Endereços de IRQ         95           Endereços de IRQ         95           Endereços de E/S         95           Estrutura de E/S         95           DMA         96           UNIDADE E - TIPOS DE ORGANIZAÇÃO DE COMPUTADORES         101           Arquiteturas paralelas         102 |                                                  |      |

| Taxa de transferência Arquitetura física de sistemas computacionais  21  UNIDADE B - UNIDADE CENTRAL DE PROCESSAMENTO  Execução de programas Clock 34  Arquitetura do processador 36  Execução de instruções Programação de processador 40  Processador hipotético 40  UNIDADE C - SISTEMA DE MEMÓRIA 41  Hierarquia de memórias 46  Memória ROM 46  Memória RAM 46  Memória Cache 47  Memória secundária  47  UNIDADE D - DISPOSITIVOS DE ENTRADA E SAÍDA 53  Categoria de dispositivos de E/S Endereços de I/O Barramentos de E/S Estrutura de E/S DMA 95  ESTRUTURA DE ORGANIZAÇÃO DE COMPUTADORES 101  Arquiteturas paralelas 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                  |      |

| Arquitetura física de sistemas computacionais  UNIDADE B - UNIDADE CENTRAL DE PROCESSAMENTO  Execução de programas  Clock  Arquitetura do processador  Execução de instruções  Programação de processador  Processador hipotético  46  UNIDADE C - SISTEMA DE MEMÓRIA  Hierarquia de memórias  Memória ROM  Memória RAM  Memória Cache  Memória secundária  UNIDADE D - DISPOSITIVOS DE ENTRADA E SAÍDA  Categoria de dispositivos de E/S  Endereços de I/O  Barramentos de E/S  Estrutura de E/S  DMA  UNIDADE E - TIPOS DE ORGANIZAÇÃO DE COMPUTADORES  Arquiteturas paralelas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Taxa de transferência                            | 21   |

| Execução de programas   33   33   33   34   34   34   34   3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Arquitetura física de sistemas computacionais    | 21   |

| Execução de programas   33   33   33   34   34   34   34   3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | UNIDADE B - UNIDADE CENTRAL DE PROCESSAMENTO     | 31   |

| Clock       34         Arquitetura do processador       36         Execução de instruções       39         Programação de processador       44         Processador hipotético       46         UNIDADE C - SISTEMA DE MEMÓRIA       61         Hierarquia de memórias       64         Memória ROM       66         Memória RAM       69         Memória cache       76         Memória secundária       82         UNIDADE D - DISPOSITIVOS DE ENTRADA E SAÍDA       93         Categoria de dispositivos de E/S       95         Endereços de IRQ       95         Endereços de I/O       95         Barramentos de E/S       97         Estrutura de E/S       96         DMA       96         UNIDADE E - TIPOS DE ORGANIZAÇÃO DE COMPUTADORES       103         Arquiteturas paralelas       102                                                                                                                                                                                                                                                                                                                 |                                                  |      |

| Arquitetura do processador       36         Execução de instruções       38         Programação de processador       44         Processador hipotético       46         UNIDADE C - SISTEMA DE MEMÓRIA       61         Hierarquia de memórias       64         Memória ROM       66         Memória RAM       69         Memória Secundária       82         UNIDADE D - DISPOSITIVOS DE ENTRADA E SAÍDA       93         Categoria de dispositivos de E/S       95         Endereços de IRQ       95         Endereços de I/O       97         Barramentos de E/S       97         Estrutura de E/S       96         DMA       96         UNIDADE E - TIPOS DE ORGANIZAÇÃO DE COMPUTADORES       103         Arquiteturas paralelas       102                                                                                                                                                                                                                                                                                                                                                                       | Clock                                            | 34   |

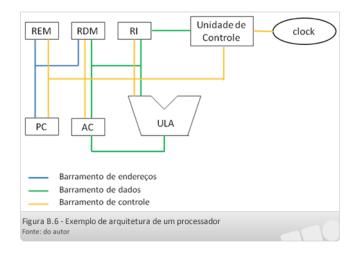

| Execução de instruções Programação de processador Processador hipotético  UNIDADE C - SISTEMA DE MEMÓRIA Hierarquia de memórias Memória ROM Memória RAM Memória RAM Memória Cache Memória secundária  UNIDADE D - DISPOSITIVOS DE ENTRADA E SAÍDA Categoria de dispositivos de E/S Endereços de IRQ Endereços de I/O Barramentos de E/S Estrutura de E/S DMA  UNIDADE E - TIPOS DE ORGANIZAÇÃO DE COMPUTADORES Arquiteturas paralelas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Arquitetura do processador                       | 36   |

| Programação de processador 44 Processador hipotético 46  UNIDADE C - SISTEMA DE MEMÓRIA 61  Hierarquia de memórias 64  Memória ROM 66  Memória RAM 65  Memória Cache 78  Memória secundária 82  UNIDADE D - DISPOSITIVOS DE ENTRADA E SAÍDA 93  Categoria de dispositivos de E/S 95  Endereços de IRQ 95  Endereços de I/O 97  Barramentos de E/S 97  Estrutura de E/S 97  Estrutura de E/S 98  DMA 98  UNIDADE E - TIPOS DE ORGANIZAÇÃO DE COMPUTADORES 102  Arquiteturas paralelas 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                  |      |

| UNIDADE C - SISTEMA DE MEMÓRIA  Hierarquia de memórias  Memória ROM  Memória RAM  Memória Cache  Memória secundária  UNIDADE D - DISPOSITIVOS DE ENTRADA E SAÍDA  Categoria de dispositivos de E/S  Endereços de IRQ  Endereços de I/O  Barramentos de E/S  Estrutura de E/S  DMA  UNIDADE E - TIPOS DE ORGANIZAÇÃO DE COMPUTADORES  Arquiteturas paralelas  102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Programação de processador                       | 4.4  |

| Hierarquia de memórias 64  Memória ROM 66  Memória RAM 69  Memória Cache 78  Memória secundária 82  UNIDADE D - DISPOSITIVOS DE ENTRADA E SAÍDA 93  Categoria de dispositivos de E/S 95  Endereços de IRQ 95  Endereços de I/O 97  Barramentos de E/S 97  Estrutura de E/S 97  Estrutura de E/S 97  UNIDADE E - TIPOS DE ORGANIZAÇÃO DE COMPUTADORES 102  Arquiteturas paralelas 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Processador hipotético                           | 46   |

| Hierarquia de memórias 64  Memória ROM 66  Memória RAM 69  Memória Cache 78  Memória secundária 82  UNIDADE D - DISPOSITIVOS DE ENTRADA E SAÍDA 93  Categoria de dispositivos de E/S 95  Endereços de IRQ 95  Endereços de I/O 97  Barramentos de E/S 97  Estrutura de E/S 97  Estrutura de E/S 97  UNIDADE E - TIPOS DE ORGANIZAÇÃO DE COMPUTADORES 102  Arquiteturas paralelas 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | UNIDADE C - SISTEMA DE MEMÓRIA                   | 61   |

| Memória ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                  |      |

| Memória RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                  |      |

| Memória Cache Memória secundária  UNIDADE D - DISPOSITIVOS DE ENTRADA E SAÍDA Categoria de dispositivos de E/S Endereços de IRQ Endereços de I/O Barramentos de E/S Estrutura de E/S DMA  UNIDADE E - TIPOS DE ORGANIZAÇÃO DE COMPUTADORES  Arquiteturas paralelas  102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Memória RAM                                      | 69   |

| Memória secundária 82  UNIDADE D - DISPOSITIVOS DE ENTRADA E SAÍDA 93  Categoria de dispositivos de E/S 95  Endereços de IRQ 95  Endereços de I/O 97  Barramentos de E/S 97  Estrutura de E/S 98  DMA 98  UNIDADE E - TIPOS DE ORGANIZAÇÃO DE COMPUTADORES 102  Arquiteturas paralelas 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Memória Cache                                    | 78   |

| Categoria de dispositivos de E/S 95 Endereços de IRQ 95 Endereços de I/O 97 Barramentos de E/S 97 Estrutura de E/S 98 DMA 98 UNIDADE E - TIPOS DE ORGANIZAÇÃO DE COMPUTADORES 101 Arquiteturas paralelas 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Memória secundária                               | 82   |

| Categoria de dispositivos de E/S 95 Endereços de IRQ 95 Endereços de I/O 97 Barramentos de E/S 97 Estrutura de E/S 98 DMA 98 UNIDADE E - TIPOS DE ORGANIZAÇÃO DE COMPUTADORES 101 Arquiteturas paralelas 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | UNIDADE D - DISPOSITIVOS DE ENTRADA E SAÍDA      | 93   |

| Endereços de IRQ       95         Endereços de I/O       97         Barramentos de E/S       97         Estrutura de E/S       98         DMA       98         UNIDADE E - TIPOS DE ORGANIZAÇÃO DE COMPUTADORES       102         Arquiteturas paralelas       102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Categoria de dispositivos de E/S                 | 95   |

| Endereços de I/O       97         Barramentos de E/S       97         Estrutura de E/S       98         DMA       98         UNIDADE E - TIPOS DE ORGANIZAÇÃO DE COMPUTADORES       101         Arquiteturas paralelas       102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                  |      |

| Barramentos de E/S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                  |      |

| Estrutura de E/S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                  |      |

| UNIDADE E - TIPOS DE ORGANIZAÇÃO DE COMPUTADORES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Estrutura de E/S                                 | 98   |

| Arquiteturas paralelas102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DMA                                              | 98   |

| Arquiteturas paralelas102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | UNIDADE E - TIPOS DE ORGANIZAÇÃO DE COMPUTADORES | 101  |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | · ·                                              | 4.05 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                  |      |

GUIA DIDÁTICO

### **APRESENTAÇÃO**

### Prezado (a) aluno (a),

Bem-vindo(a) ao espaço de estudo da Disciplina de Arquitetura e Organização de Computadores.

Ao final desta disciplina você deverá será capaz de compreender a arquitetura e a organização dos computadores através do estudo das características e funcionalidades de seus componentes.

Nesta disciplina, estudaremos as características e funcionalidades de componentes, visando compreender a arquitetura e a organização de computadores. Ela também se utiliza de conceitos de Fundamentos Matemáticos da Computação e elementos de Lógica.

Nas unidades, serão abordados os seguintes conteúdos: Conceitos básicos, Unidade Central de Processamento, Sistema de memória, Entrada e saída e Tipos de organização de computadores.

Através dela, pretende-se prover a base teórica sobre o funcionamento dos componentes e a arquitetura que formam o computador, alinhando-se com conceitos trabalhados em disciplinas como Montagem e Manutenção de Computadores, Sistemas Operacionais e outras que referenciarem o funcionamento do computador em seus conteúdos.

Bom trabalho para todos!

### **Objetivo Geral**

Compreender a arquitetura e a organização dos computadores através do estudo das características e funcionalidades de seus componentes.

### **Habilidades**

- Conhecer os conceitos básicos relativos ao funcionamento de computadores.

- Compreender o funcionamento dos componentes da Unidade Central de Processamento.

- Identificar os tipos de memória que compõem o sistema de memórias existente, bem como suas características.

- Conhecer os dispositivos de entrada e saída e a forma como realizam suas tarefas.

- Reconhecer os diferentes tipos de organização de computadores.

### Metodologia

A disciplina será desenvolvida em 60h através do Ambiente Virtual de Aprendizado Moodle. Nele, serão disponibilizados os materiais utilizados na disciplina, contando ainda com recursos de fórum, e-mail, textos de apoio e exercícios on-line.

### **Avaliação**

A avaliação se dará mediante a participação nos fóruns e a realização das atividades propostas, tanto presenciais como a distância.

### Programação

### Primeira semana:

As atividades a serem desenvolvidas na primeira semana são:

- 1. Leitura e estudo do Conteúdo: Conceitos básicos

- 2. Realização de Atividades.

- 3. Fórum de discussão para dúvidas.

### Segunda semana:

As atividades a serem desenvolvidas na segunda semana são:

- 1. Leitura e estudo do Conteúdo: Unidade Central de Processamento

- 2. Realização de Atividades.

- 3. Participação em Fórum de discussão.

### Terceira semana:

As atividades a serem desenvolvidas na terceira semana são:

- 1. Leitura e estudo do Conteúdo: Processador hipotético.

- 2. Realização de Atividades.

- 3. Fórum de discussão para dúvidas.

### Quarta semana:

As atividades a serem desenvolvidas na quarta semana são:

- 1. Leitura e estudo do Conteúdo: Simulador de processador.

- 2. Realização de Atividades.

- 3. Fórum de discussão para dúvidas.

### Quinta semana:

As atividades a serem desenvolvidas na quinta semana são:

- 1. Leitura e estudo do Conteúdo: Simulador de processador.

- 2. Realização de atividades.

- 3. Fórum de discussão para dúvidas.

### Sexta semana:

As atividades a serem desenvolvidas na sexta semana são:

- 1. Leitura e estudo do Conteúdo: Hierarquia do sistema de memória.

- 2. Realização de Atividades.

- 3. Fórum de discussão para dúvidas.

### Sétima semana:

As atividades a serem desenvolvidas na sétima semana são:

- 1. Leitura e estudo do Conteúdo: Memória Principal.

- 2. Realização de Atividades.

- 3. Fórum de discussão para dúvidas.

#### Oitava semana:

As atividades a serem desenvolvidas na oitava semana são:

- 1. Leitura e estudo do Conteúdo: Memória cachê.

- 2. Realização de Atividades.

- 3. Fórum de discussão para dúvidas.

# Sul $\perp$

### Nona semana:

As atividades a serem desenvolvidas na nona semana são:

- 1. Leitura e estudo do Conteúdo: Memória Secundária.

- 2. Realização de Atividades.

- 3. Fórum de discussão para dúvidas.

### Décima semana:

As atividades a serem desenvolvidas na décima semana são:

- 1. Leitura e estudo do Conteúdo: Entrada e Saída.

- 2. Realização de Atividades.

- 3. Fórum de discussão para dúvidas.

### Décima primeira semana:

As atividades a serem desenvolvidas na décima primeira semana são:

- 1. Leitura e estudo do Conte 2. Realização de Atividades. 1. Leitura e estudo do Conteúdo: Arquiteturas paralelas e Multiprocessamento.

- 3. Fórum de discussão para dúvidas.

### Décima segunda semana:

As atividades a serem desenvolvidas na décima segunda semana são:

1. Participação em fórum de discussão.

### Referências

CARTER, Nicholas. **Arquitetura de Computadores**. São Paulo: Bookman, 2003.

HENNESSY, John L. Arquitetura de Computadores: uma abordagem quantitativa. 3ª ed. Rio de Janeiro: Campus, 2003.

MORIMOTO, Carlos Eduardo. Hardware, o guia definitivo. Porto Alegre: Sul Editores, 2009.

MONTEIRO, Mário A. Introdução à organização de computadores. 5ª ed.. Rio de Janeiro: LTC, 2007.

PATTERSON, D. A.; HENNESSY, J. L. Projeto e Organização de Computadores: A Interface Hardware/Software. 3ª ed.. Rio de Janeiro: Campus/Elsevier, 2005.

STALLINGS, W. Arquitetura e Organização de Computadores. 5ª ed.. São Paulo: Prentice Hall, 2002.

TANENBAUM, A. S. Organização Estruturada de Computadores. 5ª ed.. Prentice-Hall, 2006.

TORRES, Gabriel. Hardware: curso completo. 4ª ed. Rio de Janeiro: Axcel Books, 2001.

VASCONCELOS, Laércio. Hardware na prática. Rio de Janeiro: edição do autor, 2007.

WEBER, Raul Fernando. Arquitetura de computadores pessoais. Porto Alegre: Sagra Luzzatto, 2001.

WEBER, Raul Fernando. Fundamentos de arquitetura de computadores. Porto Alegre: Bookman; UFRGS, 2008.

### **Currículo Professor-Autor**

Possui graduação em Ciência da Computação pela Universidade de Passo Fundo (2003), Especialização em Informática Aplicada à Educação (2005) e Formação Pedagógica de Docentes para atuação na Educação Profissional (2005) - Antigo Esquema I, ambos pela mesma instituição. É mestrando em Educação pela Universidade de Passo Fundo e atualmente é professor do Instituto Federal Sul-Riograndense (IF Sul), atuando na graduação e ensino técnico. Tem experiência na área de Ciência da Computação, atuando principalmente nos seguintes temas: informática na educação, ensino técnico, recursos didático-pedagógicos, objetos de aprendizagem, ensino-aprendizagem e interatividade.

Lattes: <a href="http://lattes.cnpq.br/2047240300453280">http://lattes.cnpq.br/2047240300453280">http://lattes.cnpq.br/2047240300453280</a> >

**Conceitos básicos**

Unidade A **Arq**uitetura e Organização de Computadores

### **CONCEITOS BÁSICOS**

### Introdução:

Antes de iniciarmos o nosso módulo, observe a seguinte imagem:

Com certeza muitos conhecem este elemento, é um modelo de placa-mãe que encontramos em nossos computadores. Mas você consegue identificar os componentes que são conectados nela?

Podemos destacar, dentre os componentes que podemos encontrar conectados em uma placa-mãe, o processador, módulos de memória RAM, disco rígido, placa de vídeo, placas de expansão, etc.

Sabemos que cada um dos componentes citados acima desempenha um papel específico no funcionamento do computador. Mas você sabe como cada um deles funciona internamente para desempenhar suas funções?

Vivemos em uma sociedade rodeada pelas mais diversas tecnologias que são utilizadas nas mais variadas atividades. Assim, "em relação ao número de usuários e de unidades instaladas, computadores pessoais são, sem dúvida, os computadores mais populares. Seu grande sucesso deve-se ao baixo custo, à flexibilidade de serem adaptados a um grande número de aplicações, à grande quantidade de software disponível e à facilidade de encontrar profissionais familiarizados com sua arquitetura" (WEBER, 2008, p. 1). Para a compreensão sobre o funcionamento dos computadores, é necessário o estudo dos elementos que compõem sua arquitetura, sendo importante para aqueles que o utilizam que conheçam as relações existentes internamente e entendam o papel dessas no desempenho da máquina.

### Informação

A finalidade básica de um computador é a de realizar operações com informações em formato digital. Agora, para entendermos o porquê das informações serem digitais e entendermos o que isso significa, devemos distinguir os tipos de informações existentes.

### Informação analógica

Na natureza, todo tipo de informação pode assumir qualquer valor em um intervalo de -  $\infty$  a +  $\infty$ . É possível distinguir uma cor verde que esteja um pouco mais clara de outro tom de verde, em uma variação quase infinita de tons de mesma cor, do mais claro até o mais escuro. Pode-se distinguir um som mais alto do que outro, assim como perceber quanto um ambiente está mais claro do que outro. Todo esse tipo de informação é conhecido como *informação analógica* (TORRES, 2001). Os sinais analógicos citados são lidos de forma direta, sem que seja necessário ocorrer qualquer tipo de decodificação complexa para compreendê-los.

### **Atenção**

Situação: uma música gravada em uma fita cassete.

Após, passado certo tempo, a mesma música fica com um som mais "abafado", com "chiados" e "estalos"; que são os ruídos.

A razão disso se deve ao fato de que a informação da música na fita cassete foi gravada de maneira analógica, na hora de reproduzir a música, o gravador simplesmente achou que os ruídos fizessem parte dela.

Isso porque, como a informação foi gravada analogicamente, poderia assumir qualquer valor, inclusive o valor "ruído".

(TORRES, 2001)

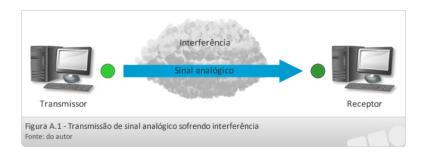

O sinal armazenado se degrada com o tempo, e existe sempre certa perda de qualidade ao se fazer cópias. No caso de uma fita, o aparelho interpreta os ruídos gerados pela degradação como parte da música. Quando em uma transmissão, caso o sinal enviado sofra alguma interferência, torna-se difícil identificar se houve alguma alteração ou não no caminho entre o emissor e o receptor, conforme figura abaixo, onde um tom de verde foi enviado e um tom de verde foi recebido, embora de tons diferentes, sendo difícil identificar a alteração:

### Informação digital

Dispositivos eletrônicos no processamento de informações trabalham com o sistema binário. No sistema binário, ao contrário do sistema de numeração decimal (que utilizamos), só há dois algarismos: "0" e "1". Nisto há uma grande vantagem: qualquer valor diferente desses será completamente desprezado pelo circuito eletrônico, gerando confiabilidade e funcionalidade. Esse sistema também é chamado de sistema digital. Cada algarismo binário é chamado de *bit* (contração de *binary digit*). (TORRES, 2001).

### Atenção

Situação: uma música gravada em uma fita DAT (Digital Audio Tape, que grava informações digitalmente).

Com o passar do tempo estaria, como uma fita cassete analógica, cheia de interferências em sua camada magnética, na forma de ruído.

Mas por ter sido gravada sob a forma de informações digitais, a música está codificada sob a forma de vários "0"s e "1"s.

Qualquer outro valor diferente de "0" ou "1" será simplesmente ignorado pelo aparelho reprodutor.

(TORRES, 2001)

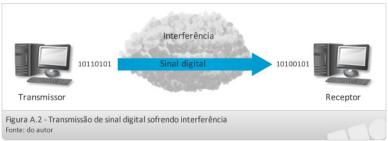

A vantagem do sistema digital sobre o analógico é que as informações são gravadas em forma de números. No caso de um CD, por exemplo, o que há gravado não são músicas ou sons, mas sim números. Com isso, há como se utilizar mecanismos de correção de erros a fim de verificar a integridade dos dados, tornando-o mais confiável (TORRES, 2001). No caso de uma transmissão, caso o sinal enviado sofra alguma interferência, é possível identificar se houve alguma alteração ou não no caminho entre o emissor e o receptor, visto que os valores de "0"s e "1"s podem ser conferidos, conforme figura abaixo, onde existe uma diferença entre o conjunto de bits enviados e o conjunto de bits recebidos, facilitando a identificação:

### **Números binários**

Conjuntos de algarismos binários (bits) formam palavras binárias, sendo que cada casa binária só poderá ser preenchida com dois algarismos (0 ou 1), enquanto cada casa decimal pode ser preenchida com dez algarismos (de 0 a 9). As palavras binárias recebem nomes especiais conforme a quantidade de bits utilizada pelas mesmas, representando uma variação de números bastante definida: (TORRES, 2001)

- Nibble: 4 bits (24 = 16 variações)

- Byte: 8 bits (28 = 256 variações)

- Word: 16 bits (216 = 65.536 variações)

- Double Word = 32 bits (232 = 4.294.967.296 variações)

- Quad Word = 64 bits (264 = 18.446.744.073.709.551.616 variações)

O número máximo que pode ser expresso por palavra binária é determinado pela quantidade de bits que ela formada, sendo assim, com um byte é possível representar 256 números (28), por exemplo. Os números "inteiros" em binário, pelo fato de ser utilizada a base 2 ao invés da base 10, quando representados em decimal parecem "quebrados". Por exemplo, 1.024 é um número inteiro em binário, pois representa 27, sendo que o valor "inteiro" equivalente a ele em decimal seria 1000.

O sufixo K (kilo-), que, em decimal, representa 1.000 vezes (como em Km e Kg), em binário representa 2<sup>10</sup> vezes (1.024). Logo, 1 Kbyte representa 1.024 bytes, 2 Kbytes representam 2.048 bytes e assim sucessivamente. Do mesmo modo, o sufixo M (mega-) representa 2<sup>20</sup> vezes (1.048.576) e o sufixo G (giga-) representa 2<sup>30</sup> vezes (1.073.741.824), diferenciando-se completamente da representação decimal (TORRES, 2001, p. 7). Conforme tabelas a seguir:

| Potência de 2 |     |                                   |  |  |

|---------------|-----|-----------------------------------|--|--|

| Kilo (K)      | 210 | 1.024                             |  |  |

| Mega (M)      | 220 | 1.048.576                         |  |  |

| Giga (G)      | 230 | 1.073.741.824                     |  |  |

| Tera (T)      | 240 | 1.099.511.627.776                 |  |  |

| Peta (P)      | 250 | 1.125.899.906.843.624             |  |  |

| Exa (E)       | 260 | 1.152.921.504.607.870.976         |  |  |

| Zeta (Z)      | 270 | 1.180.591.620.718.458.879.424     |  |  |

| Yotta (Y)     | 280 | 1.208.925.819.615.701.892.530.176 |  |  |

Tabela A.1 – Representação dos sufixos em binário

| Potência de 10 |           |                                    |  |  |

|----------------|-----------|------------------------------------|--|--|

| Kilo (K)       | $10^{3}$  | 1.000                              |  |  |

| Mega (M)       | $10^{6}$  | 1.000.000                          |  |  |

| Giga (G)       | 10°       | 1.000.000.000                      |  |  |

| Tera (T)       | 1012      | 1.000.000.000.000                  |  |  |

| Peta (P)       | $10^{15}$ | 1.000.000.000.000                  |  |  |

| Exa (E)        | $10^{18}$ | 1. 000.000.000.000.000             |  |  |

| Zeta (Z)       | 1021      | 1. 000.000.000.000.000.000         |  |  |

| Yotta (Y)      | 1024      | 1. 000.000.000.000.000.000.000.000 |  |  |

Tabela A.2 – Representação dos sufixos em decimal

O byte é a palavra binária mais utilizada, principalmente porque os microprocessadores passaram a ser largamente utilizados (década de 1970) com modelos de oito bits. Um aspecto fundamental é o de representar as palavras binárias byte e bit. Enquanto abreviamos bit com "b" (b minúsculo), abreviamos byte com "B" (b maiúsculo). Assim, 1 KB é a representação de um kilobyte (1.024 bytes = 8.192 bits), enquanto 1 Kb é a representação de um kilobit (1.024 bits). (TORRES, 2001, p. 9)

### Clock

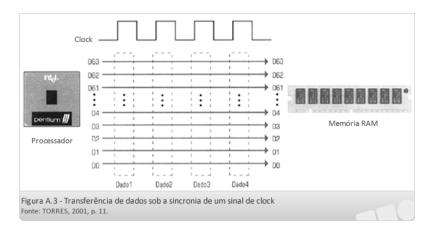

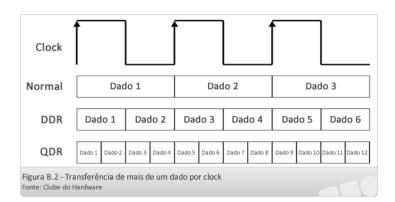

A transmissão de dados no computador, entre um dispositivo receptor e um dispositivo transmissor, é controlada por um sinal de controle chamado clock. Esse sinal é usado para sincronizar o transmissor com o receptor, isto é, para informar ao receptor que um dado está sendo transmitido (TORRES, 2001). Na figura abaixo, é demonstrado um clock com 4 ciclos, sendo que em cada um deles é enviado um dado do processador para a memória RAM:

A frequência do clock (quantidade de pulsos por segundo) determina a velocidade da transmissão (frequência de operação). Esta frequência é medida em Hertz (Hz). Por exemplo, um clock de 100 MHz significa que em um segundo temos 100 milhões de pulsos e em cada um desses pulsos existe a possibilidade da transmissão de dados.

Como em cada pulso de clock um dado pode ser transmitido, aumentando-se a frequência do clock, aumenta-se a velocidade com que os dados são transmitidos.

### Atenção

Os sistemas de clock utilizados para a comunicação entre os dispositivos são independentes.

A comunicação do disco rígido com a placa-mãe utiliza um sistema de clock, assim como a comunicação da placa de vídeo com a placa-mãe e do processador com a memória RAM.

### Transmissão de dados

Cada dispositivo digital trabalha com um determinado número de bits, sendo que o canal de comunicação deste dispositivo transmite e recebe essa quantidade de bits por vez. (TORRES, 2001)

### **Atenção**

Cada dispositivo só pode comunicar-se com dispositivos que manipulem a mesma quantidade de bits. Um dispositivo de 8 bits somente se comunica diretamente com outro dispositivo de 8 bits, assim como um de 32 bits somente se comunica diretamente com outro de 32 bits, e assim sucessivamente.

A comunicação entre dispositivos ocorre de duas formas: transmissão paralela ou transmissão em série.

### Transmissão Paralela

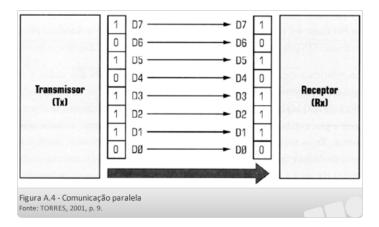

Neste tipo de transmissão todos os bits que o dispositivo transmissor é capaz de manipular são transmitidos simultaneamente ao receptor, através de vias (caminhos por onde os dados trafegam) paralelas. Conforme pode ser vista na figura:

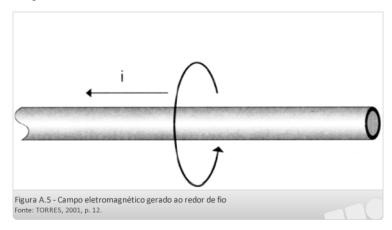

### Interferência eletromagnética

Na transmissão paralela pode ocorrer o problema de ruído interferindo na transmissão dos dados. Isso se deve ao fato de que quando uma corrente elétrica passa por um fio condutor é criado um campo eletromagnético ao redor e, se esse campo eletromagnético for muito forte, será gerado um ruído no fio ao lado, corrompendo a informação transmitida. Quanto maior for a frequência de operação do dispositivo, maior será a possibilidade de ocorrer ruído.

### Atenuação

Outra situação que pode ocorrer é de o sinal transmitido enfraquecer na medida em que trafega no fio condutor, sendo que quanto mais longo for o fio, mais fraco fica o sinal ao longo da distância percorrida, tornando-se atenuado.

### Transmissão em Série

Este tipo de transmissão é caracterizado por enviar um bit por vez. Como ela possui um único fio condutor utilizado para transmitir as informações, sofre menos com os problemas de ruído e de atenuação. Dessa forma, é possível atingir uma frequência de operação mais alta.

### Transmissão em Série Síncrona

Nela, é utilizado um fio independente para a transmissão do sinal de clock, que é usado pelo receptor para saber onde começa e onde termina cada dado que está sendo transmitido e outro para o envio e recebimento dos dados (TORRES, 2001).

### Transmissão em Série Assíncrona

Nela, o mesmo canal onde os dados são transmitidos é usado para a transmissão dos sinais de sincronismo entre o transmissor e o receptor. São transmitidos dois sinais de sincronismo, chamados start bit e stop bit, indicando, respectivamente, o início e o fim da transmissão de um grupo de bits (TORRES, 2001).

### Taxa de Transferência

Além do clock, a velocidade de transmissão depende também da quantidade de bits que são transmitidos por vez (TORRES, 2001). Considere os 3 dispositivos abaixo:

- Dispositivo de 64 bits com clock de 100 MHz

- Dispositivo de 128 bits com clock de 50 MHz

- Dispositivo de 32 bits com clock de 200 MHz

Calculando a taxa de transferência máxima teórica através da fórmula

Taxa de transferência = clock (em Hz) x quantidade de bits ÷ 8

Podemos verificar que os três dispositivos, apesar de terem quantidade de bits e frequência de clock diferentes apresentam a mesma taxa de transferência máxima teórica de 800 MB/s. Dessa forma, podemos constatar que ambos os fatores (frequência de operação e quantidade de bits) influenciam na transmissão de dados.

### **Atenção**

A velocidade de transmissão paralela é padronizada em bytes por segundo (B/s), assim como a transmissão em série é em bits por segundo (b/s).

### Arquitetura física de sistemas computacionais

Antes de conhecermos os componentes que formam a arquitetura dos sistemas computacionais, vamos conhecer a história da informática até chegar ao que conhecemos hoje, para isso, assista ao vídeo disponível em:

http://www.youtube.com/watch?v=F3qWg1JBPZg.

### Histórico

Máquinas de calcular e computadores vêm sendo inventados e desenvolvidos ao longo da história da humanidade (WEBER, 2004), conforme pode ser visto no breve histórico a seguir:

### **Blaise Pascal**

Em 1642 ele desenvolve a primeira máquina calculadora mecânica, a pascaline, que era não programável e utilizada para a realização de somas e subtrações;

### **Charles Babbage**

Ele projeta dois computadores que, embora não tenham sido concluídos, resultam em consideráveis avanços científicos na época. Em 1823 ele projeta o "Dispositivo Diferencial" para a resolução automática de tabelas

matemáticas. Em 1834 ele projeta o "Dispositivo analítico" com intuito de que realizasse qualquer operação matemática automaticamente, sendo que nela já havia módulos de armazenamento (memória) e uma unidade operadora com a entrada e a saída de dados ocorrendo através de cartões perfurados e com a possibilidade de alterar a sequência dos comandos executados (programável). (WEBER, 2004).

Os principais avanços tecnológicos da computação podem ser vistos na imagem abaixo:

| Data | Inventor: máquina             | Capacidade                                     | Inovações técnicas                                                  |

|------|-------------------------------|------------------------------------------------|---------------------------------------------------------------------|

| 1642 | Pascal: Calculadora           | adição, subtração                              | transferência automática de vai-um:<br>representação em complemento |

| 1671 | Leibnitz: Calculadora         | adição, subtração,<br>multiplicação, divisão   | mecanismo para multiplicação e divisão                              |

| 1827 | Babbage: Difference<br>Engine | avaliação polinomial por<br>diferenças finitas | operação automática com diversos passos                             |

| 1834 | Babbage: Analytical<br>Engine | computador de<br>propósitos gerais             | mecanismo automático de controle de sequência (programa)            |

| 1941 | Zuse: Z3                      | computador de<br>propósitos gerais             | primeiros computadores de propósitos<br>gerais operacionais         |

| 1944 | Aiken: Harward Mark I         | computador de<br>propósitos gerais             | primeiros computadores de propósitos<br>gerais operacionais         |

Figura A.7 - Avanços tecnológicos. Fonte: Weber, 2004

O primeiro computador eletrônico de propósitos gerais foi provavelmente o ENIAC (Eletronic Numerical Integrator and Calculator), construído entre 1943 e 1946 devido à necessidade de construir tabelas balísticas por interesse do sistema militar americano. Era uma máquina de 30 toneladas, contendo 18000 válvulas (WEBER, 2004).

Com o avanço da pesquisa e o consequente desenvolvimento tecnológico ao longo do tempo, a tecnologia e os estilos usados na construção e programação de computadores formaram várias gerações de computadores (WEBER, 2004), conforme imagem:

| Geração                    | Tecnologias                                               | Característica de hardware                                   | Característica de software                                                          | Exemplo                   |

|----------------------------|-----------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------|

| 1 <sup>a</sup> (1946-1954) | válvulas, memórias de<br>tubos catódicos                  | aritmética de ponto fixo                                     | linguagem de máquina,<br>linguagem assembler                                        | IAS, UNIVAC               |

| 2ª<br>(1955-1964)          | transistores, núcleos<br>de ferrite, discos<br>magnéticos | ponto flutuante,<br>registrador índice,<br>processadores E/S | linguagens de alto nível,<br>bibliotecas de rotinas,<br>processamento em lote       | IBM7094<br>CDC1604        |

| 3ª<br>(1965-1974)          | circuitos integrados<br>(SSI e MSI)                       | microprogramação,<br>pipeline, memória cache                 | multiprogramação,<br>multiprocessamento,<br>sistema operacional,<br>memória virtual | IBM S/360;<br>DEC PDP-8   |

| 4ª(1975-?)                 | circuitos LSI, memórias<br>semicondutoras                 |                                                              |                                                                                     | Amdahl 470;<br>Intel 8748 |

Figura A.8 - Gerações de computadores

### Modelo de von Neumann

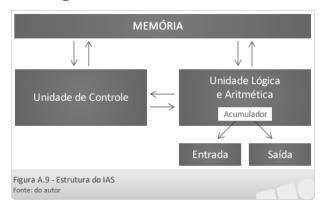

Em 1946, von Neumann e sua equipe iniciaram o projeto de um novo computador de programa armazenado: o computador IAS. Ela usava uma memória principal de acesso randômico, o que permitia o acesso a uma palavra inteira em uma palavra inteira em uma única operação. Essa máquina acabou por influenciar os projetos subsequentes de outras máquinas (WEBER, 2004).

### Atenção

#### Blocos básicos:

- uma unidade de processamento central, para execução de operações aritméticas e lógicas.

- uma unidade de controle de programa, para determinar o sequenciamento das instruções a serem executadas e gerar os sinais de controle para as outras unidades. Esses sinais determinam as ações a serem executadas.

- uma unidade de memória principal.

- uma unidade de entrada e saída.

(WEBER, 2004)

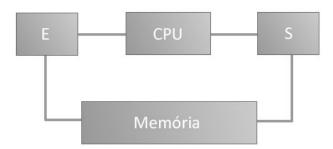

Ele apresentava sua estrutura da seguinte maneira:

### Princípios básicos

Cada computador tem um conjunto de operações e convenções para determinar as posições dos dados com os quais a operação será realizada.

As ações a serem executadas em um computador são definidas por instruções, que são compostas por:

- Operação: especifica a operação que será desempenhada.

- Operandos: indicam a posição dos dados com os quais a operação será realizada.

Um **programa** é formado por uma sequência pré-determinada de instruções. O programa e seus dados ficam armazenados na memória da máquina.

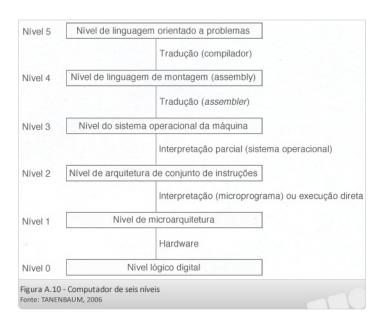

Para que um programa armazenado na memória seja processado, é necessário que suas instruções sejam interpretadas. Isso se deve ao fato de que os programas são formados por instruções de uma linguagem de alto nível, mais convenientes aos programadores (digamos que seja L1), ao contrário da máquina, que trabalha com uma linguagem baseada em instruções de baixo nível (digamos que seja L0). Apesar disso, os programas escritos em L1 têm de executar em um computador programado em L0.

### Atenção

Os métodos para executar um programa L1 em L0 são os seguintes:

- Tradução: consiste em substituir cada instrução escrita no programa por uma sequência equivalente de instruções em LO. O computador executa o novo programa LO em vez do programa L1.

- Interpretação: o programa em L0 considera os programas em L1 como dados de entrada. Ele os executa examinando cada instrução por vez, executando diretamente a sequência equivalente de instruções L0.

(TANENBAUM, 2006)

A maioria dos computadores modernos apresenta dois ou mais níveis no processo de conversão entre a linguagem de programas e a do computador.

### **Níveis:**

- Nível lógico digital: composto por portas que possuem uma ou mais entradas digitais (0 ou 1) e que computam como saída alguma função dessas entradas, como E (AND), OU (OR), etc.

- Nível de microarquitetura: composto por um conjunto de registradores (que formam uma memória local) e um circuito denominado ULA (Unidade Lógica e Aritmética) que executa operações lógicas e aritméticas.

- Nível de arquitetura do conjunto de instruções: conhecido como ISA (Instructiun Set Architectue). São as instruções executadas por interpretação pelo microprograma ou pelos circuitos de execução do hardware.

- Nível de máquina de sistema operacional: caracteriza-se por ser um nível híbrido. Parte das instruções em sua linguagem também está no nível ISA, assim como existe um conjunto de novas instruções, que permitem a ele se relacionar com os níveis superiores.

- Nível da linguagem de montagem: baseado na linguagem assembly, que fornece um método para que sejam escritos programas para os níveis 1, 2 e 3 em uma forma que não seja tão desagradável quanto as linguagens de máquina real em si.

- Nível de linguagem orientado a problemas: consiste em linguagens projetadas para ser usadas por programadores de aplicações que tenham um problema a resolver. Essas linguagens costumam ser denominadas linguagens de alto nível (TANENBAUM, 2006).

### **Componentes dos sistemas computacionais**

Os circuitos eletrônicos digitais, que formam os elementos do computador, são construídos com uma pastilha de material semicondutor, chamado silício. Cada pastilha agrupa milhões de transistores.

Sistema Universidade Aberta do Brasil - UAB | IF Sul-rio-grandense

Com o avanço tecnológico, tem sido possível a construção de pastilhas de silício cada vez menores e com maior densidade, isto é, maior concentração de transistores. O motivo é diminuição das trilhas que compõem a pastilha de silício. A distância entre elas geralmente é dada em micrômetro (µm) que equivale a 10-6 (0,000001 metros), chegando aos nanômetros (nm) que equivale a 10-9 (0,000000001 metros).

### **Atenção**

Quanto menor a distância das trilhas da pastilha de silício, menos corrente é necessária para deslocar elétrons dentro das trilhas, influindo em:

- Os elétrons chegam ao destino em menos tempo.

- Maior frequência de operação (clock).

- Menor consumo elétrico.

- Menor produção de calor.

- Tensão de alimentação ("voltagem") menor.

(TORRES, 2001)

### **Componentes dos sistemas computacionais**

Os elementos básicos dos computadores relacionam-se na seguinte estrutura:

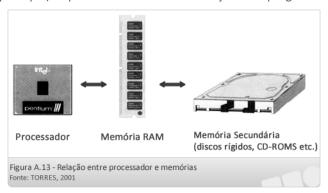

Dentre os elementos que compõem um sistema computacional atual podemos destacar:

- Placa-Mãe: é a responsável pela interconexão de todas as peças que formam o sistema computacional. Ela é

desenvolvida de modo a tornar possível conectar todos os dispositivos do computador, oferecendo conexões para

o processador, para a memória RAM, para o HD, para os dispositivos de entrada e saída, entre outros. Dois de seus

chipsets exercem importantes funções:

- Ponte norte (northbridge): interliga o processador a dispositivos rápidos como memória RAM e placa de vídeo

- Ponte sul (southbridge): interliga os demais dispositivos da máquina à ponte norte, que por sua vez faz a ligação com o processador.

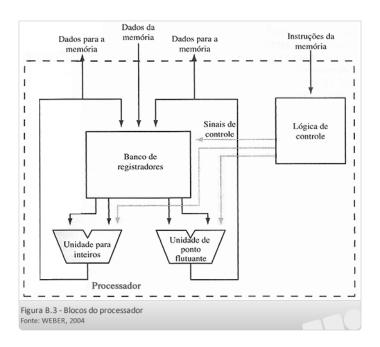

- Processador: a CPU (Central Processing Unit) ou UCP (Unidade Central de Processamento) é composta por circuitos integrados passíveis de programação, que manipulam e processam dados. Em seu processamento ele segue instruções (que compõem os programas) que se traduzem em comandos executados por ele com base em seu conjunto de instruções.

O processador entende uma quantidade finita de instruções que são listadas em uma tabela conhecida como conjunto de instruções. Cada processador pode ter um conjunto de instruções diferentes.

Memória: ela tem a função de armazenar dados e instruções dos programas, sendo estruturada na forma de uma

matriz organizada em posições, sendo que cada informação armazenada nela ocupa um endereço específico.

Quando se executa um programa, ele é transferido, normalmente, do disco rígido (memória secundária) para a

memória RAM (memória principal). O processador busca as instruções dos programas na memória RAM.

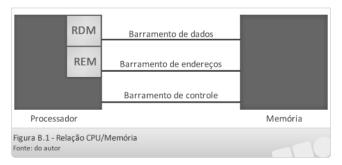

A transferência de informações entre a CPU e a memória principal ocorre através de **palavras**. A unidade palavra indica a unidade de transferência e processamento de um computador. As palavras são múltiplos de 1 byte, sendo que, se um microprocessador utilizar 32bits serão 4 bytes como tamanho da palavra.

- **Barramento**: é um caminho para a troca de dados entre circuitos, formado por um conjunto de condutores chamados de trilhas, por onde trafegam os bits. Ele apresenta as seguintes características:

- largura do barramento: número de bits transportados numa operação (ex: 32 bits).

- frequência de operação: velocidade com que os dados são transmitidos (ex: 400 MHz).

### Geralmente possui duas linhas:

- Linhas de controle: por onde são transmitidas informações de sinalização, como o tipo de operação que está sendo realizada (leitura, escrita, etc.).

- Linhas de dados: por onde trafegam instruções, operandos e endereços.

- **Dispositivos de Entrada e Saída**: os dispositivos de I/O (Input/Output) ou dispositivos de E/S (Entrada/Saída) são utilizados para comunicar o computador com o meio externo para receber dados ou responder ao processamento executado (ex: teclado, monitor, impressora, CD, pen drive, etc).

### **Arquiteturas**

Nos primórdios da informática existiam vários fabricantes diferentes e cada um desenvolvia todos os componentes de seus próprios computadores, que eram incompatíveis entre os diferentes fabricantes. Com o desenvolvimento dos computadores pessoais, surge a plataforma PC, que se trata de uma **arquitetura aberta** a qual permite o uso de componentes de diversos fabricantes e de diferentes sistemas operacionais. Essa arquitetura é baseada em padrões definidos, a partir dos quais produtores podem desenvolver seus próprios componentes, existindo assim compatibilidade entre os componentes de diferentes fabricantes. Dessa forma, ela favorece o desenvolvimento a partir da concorrência entre fabricantes, criando uma demanda maior, permitindo preços mais baixos.

Também existe a **arquitetura fechada**, que se trata de uma arquitetura restrita pelo fato de os padrões, para desenvolvimento de componentes, serem proprietários, não permitindo seu uso por outros fabricantes. Com ela, os conflitos de hardware diminuem, fazendo com que o computador apresente melhor desempenho. Geralmente são encontrados em mainframes, servidores e supercomputadores, sendo que a assistência e as peças para substituição são encontradas somente com o próprio fabricante.

### Resumo

### Ao final da presente unidade, vimos que:

- O computador trabalha com informações digitais, ao invés de informações analógicas como na natureza.

- O sistema de numeração binário é a base do sistema digital utilizado pelo computador, onde a partir de um bit (0 ou 1) temos um sistema de palavras binárias (nibble, byte, etc) e um sistema de unidades (Kbyte, MByte, etc).

- A transmissão de dados em um computador é sincronizada através do sinal de clock, que indica a frequência de operação na comunicação entre dispositivos.

- Na transmissão de dados, existem dois tipos de dispositivos: em série, que transmitem um bit por vez, e os paralelos, que transmitem um conjunto de bits por vez.

- Tanto a frequência de operação quanto a quantidade de bits influenciam na transmissão de dados.

- O modelo de von Neumann é baseado na existência de uma unidade de processamento central, uma unidade de controle de programa, uma unidade de memória principal e uma unidade de entrada e saída.

- Todo programa que é executado no computador é formado por uma sequência de instruções (formada por operação e operandos) que ficam armazenadas na memória.

- Os programas são escritos em uma linguagem de alto nível, sendo que o computador trabalha em uma linguagem de baixo nível. Para que ocorra comunicação entre elas, é necessário utilizar os métodos de tradução e de interpretação, podendo existir vários níveis nesse processo.

- A distância das trilhas da pastilha de silício influencia em série de aspectos como a distância a ser percorrida pelos elétrons, frequência de operação, consumo elétrico, etc.

- Dentre os componentes de um sistema computacional podemos destacar a placa-mãe, o processador, a memória, o barramento e os dispositivos de entrada e saída.

- Podemos encontrar dois tipos de arquiteturas de computadores atualmente: a aberta e a fechada.

### Questões de Revisão

- a) Por que os sistemas computacionais não utilizam sinal analógico ao invés de sinal digital?

- b) Em que consiste o sistema binário?

- c) Conceitue bit, Byte, Word, KByte, MByte e GByte.

- d) Diferencie transmissão paralela de transmissão em série.

- e) O que é o clock, como ele é medido e o que ele influencia na transmissão de dados?

- f) Descreva o princípio básico da arquitetura de Von Neuman e seus elementos básicos.

- g) Que problema existe entre programa e computador? Que métodos existem para resolvê-lo?

- h) Qual é o papel de uma placa-mãe? E qual é a finalidade da ponte norte e da ponte sul?

- i) Qual é a função do processador? Quais são suas características?

- j) Como funciona a memória principal?

- k) Comente sobre o barramento do computador.

- I) Qual é a importância dos dispositivos de entrada e saída?

- m) O que a distância entre as trilhas de uma partícula de silício influencia no micro?

- n) Quais são as arquiteturas de computadores existentes? Quais são suas características?

### Referências

TANENBAUM, Andrew S. **Organização Estruturada de Computadores.** 5ª ed. São Paulo: Pearson, 2006.

TORRES,, Gabriel. Hardware: curso completo. 4ª ed. Rio de Janeiro: Axcel Books, 2001.

WEBER, Raul Fernando. Arquitetura de computadores pessoais. Porto Alegre: Sagra Luzzatto, 2004.

WEBER, Raul Fernando. Fundamentos de arquitetura de computadores. Porto Alegre: Bookman; UFRGS,

2008.

### **Atividades**

- 1. Considere as seguintes afirmações:

- I. Um bit é o conjunto de 8 bytes.

- II. Na potência de 2, um Giga equivale a 230 Bytes.

- III. Uma informação, no formato digital, pode assumir qualquer valor.

- IV. Um sinal digital pode ser verificado quanto a sua integridade.

- V. O sistema binário baseia-se em dois estados de tensão em que o computador trabalha: ligado (1) e desligado (0). Estão corretas as afirmativas

- a) II, III e V.

- b) I e IV.

- c) II, IV e V.

- d) III e V.

- 2. Em relação aos sufixos binários, qual é a alternativa correta?

- a) Um GB representa 1.000.000.000 de bits.

- b) Um KB representa 1024 bytes.

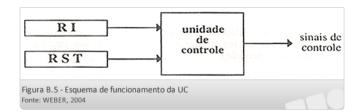

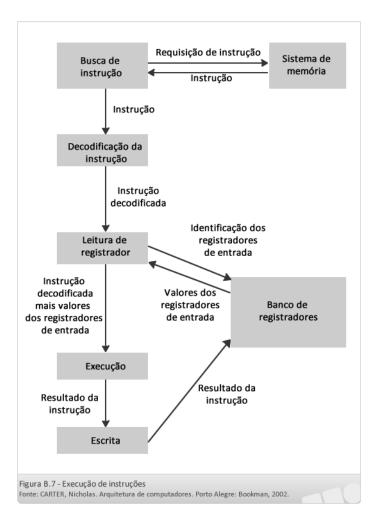

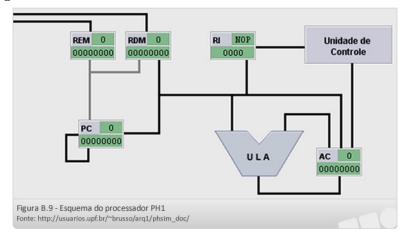

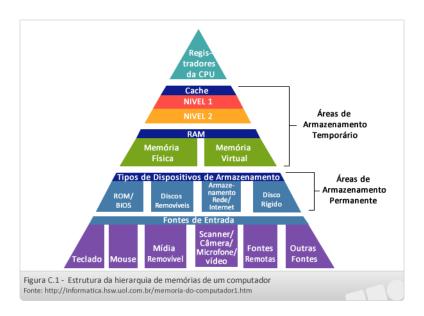

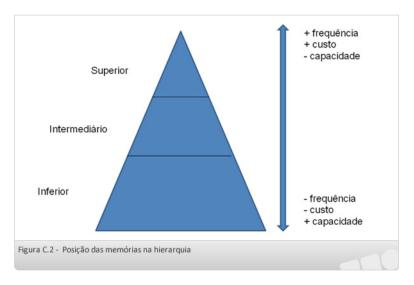

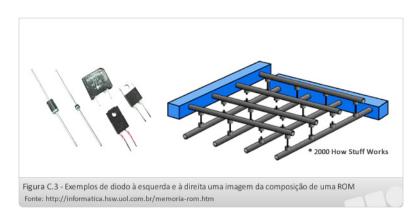

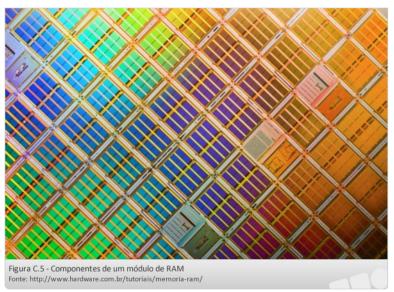

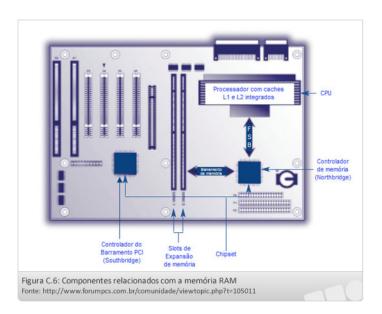

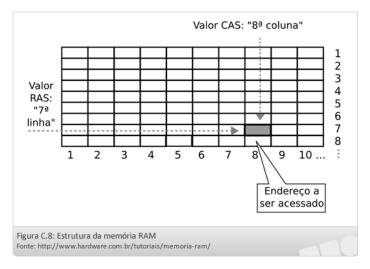

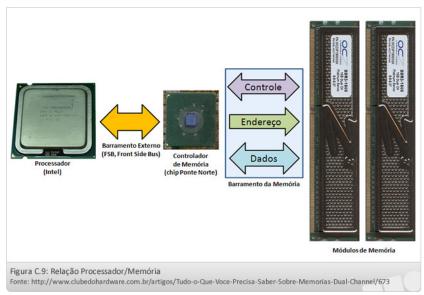

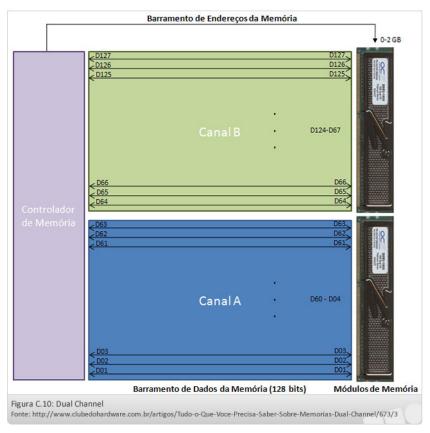

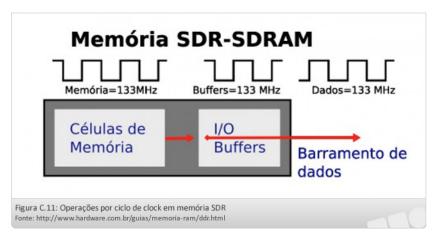

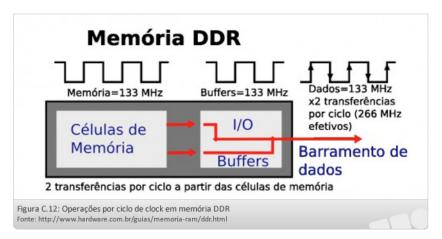

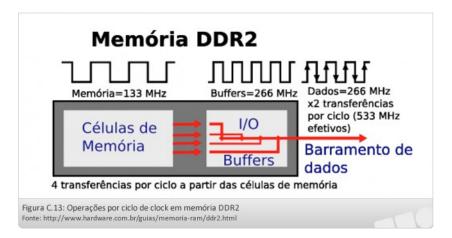

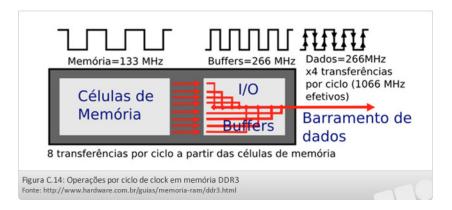

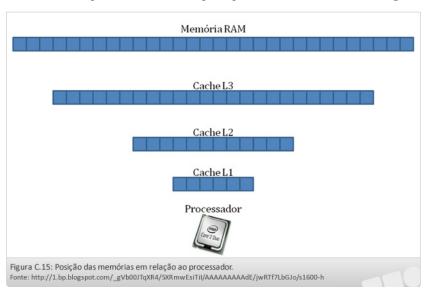

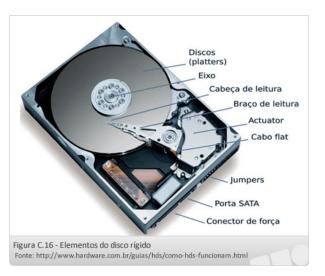

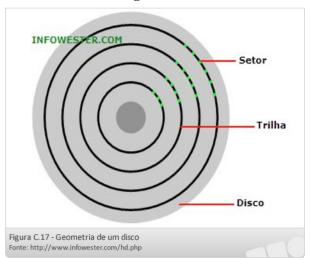

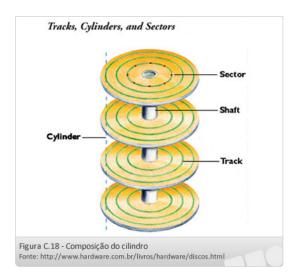

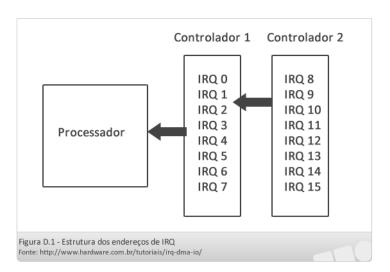

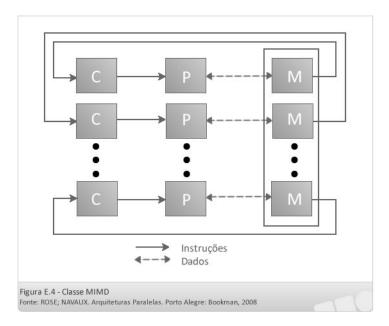

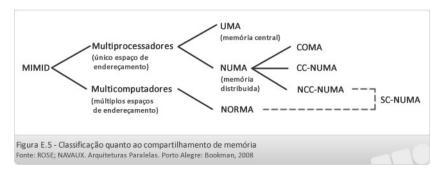

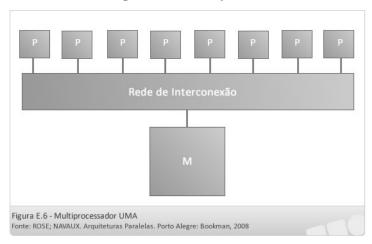

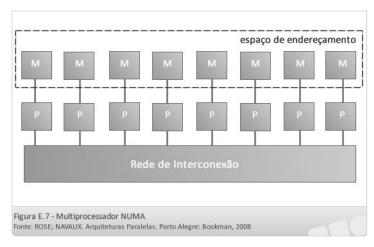

- c) Um TB representa 1.073.741.824 bytes.