B.2 Clock

O processador, no desempenho de suas atividades, necessita realizar operações internamente e também comunicar-se com os demais componentes do micro (para ler e gravar informações na memória principal, por exemplo). Segundo Torres:

Os processadores atualmente utilizam um esquema de multiplicação de clock, onde o clock do barramento local é muito inferior ao clock interno do processador. Esse esquema de multiplicação de clock foi criado porque é difícil construir placas-mãe e circuitos de apoio que consigam operar em frequências de operação tão altas como aquelas que os processadores conseguem trabalhar internamente. (2001, p. 34)

Portanto, o clock interno do processador é a frequência com a qual o processador trabalha internamente na execução de suas atividades, sendo utilizado o clock externo para a comunicação com os demais componentes do computador através da placa-mãe.

| ||||

|

B.2.1 Técnicas para minimizar a diferença de clock

Visando minimizar a diferença existente entre o clock interno e o clock externo do processador são utilizadas algumas técnicas. Uma solução envolve a utilização de memória cache (que será abordada no próximo módulo, juntamente com o sistema de memórias), que se trata de uma memória de maior velocidade de acesso que a memória principal.

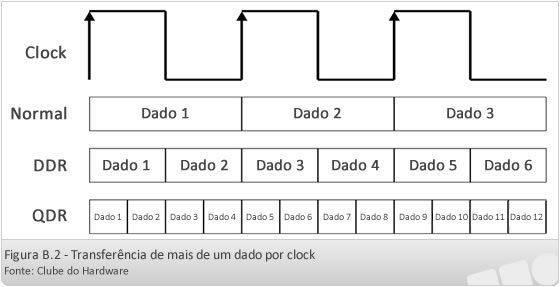

A transferência de mais de um dado por ciclo de clock também é uma técnica empregada para compensar essa diferença. Ela consiste em transferir dois dados por ciclo de clock, a chamada DDR (Dual Data Rate), assim como transferir quatro dados por ciclo de clock, a QDR (Quad Data Rate).