Introdução

Outro elemento importante do sistema de memória de um computador é a memória cache que, conforme já comentado na unidade B, executa uma importante função, intermediando a relação entre memória RAM e processador.

C.8 Memória Cache

Cache é um bloco de memória que serve para armazenar, de forma temporária, determinados dados que possivelmente serão utilizados ou que foram utilizados recentemente. Referente a ela, podemos destacar os seguintes fatores:

- tem como característica ser de acesso rápido, intermediando a relação entre quem requisita uma informação e o dispositivo que a armazena;

- tem como característica ser de acesso rápido, intermediando a relação entre quem requisita uma informação e o dispositivo que a armazena;

- busca evitar o acesso aos dispositivos de armazenamento mais lentos, armazenando os dados de forma a estarem mais próximos de quem os solicita;

- é composta por uma fila de elementos, que são cópias exatas de dados presentes em algum outro local (no caso, o local original de armazenamento). Cada elemento possui uma etiqueta que indica o local de armazenamento original (de onde ele foi copiado).

Essa técnica é empregada em diversas situações na informática, sempre com o objetivo principal de agilizar o acesso a determinadas informações que são necessárias a um determinado elemento, como:

- em processadores: onde disponibilizam dados já requisitados e outros a serem processados.

- em navegadores: armazenando localmente páginas acessadas, evitando consultas constantes à rede.

- em redes de computadores: quando o acesso externo à rede ocorre através de serviço de proxy (que compartilha a conexão/link), pode-se armazenar uma lista de sites visitados por usuários da rede.

- em discos rígidos: onde ficam armazenados os dados recentemente acessados nele.

Acesso à cache

Quando o cliente de cache deseja acessar um dado no local de armazenamento original (memória RAM, HD, Internet, etc.), primeiramente é verificado se ele não está presente na cache. Se o dado necessário for encontrado na cache com a etiqueta correspondente ao desejado, o que está na cache é enviado ao invés do original.

Nessa situação, quando o cliente acessa somente a cache , ocorre o chamado cache hit (acerto do cache), que justamente é a situação em que a informação a ser acessada é localizada na cache, evitando o acesso à mídia de armazenamento inferior na hierarquia, que consequentemente é mais lenta. A quantidade de acertos é conhecida como a taxa de acerto (hit rate ou hit ratio) da cache. Quanto maior essa taxa, melhor é o desempenho.

Por outro lado, quando a informação requerida não é localizada na cache, ocorre o cache miss (erro do cache). Dessa forma, a informação deve ser copiada do local original de armazenamento e inserida na cache, sendo disponibilizada para o acesso.

Sendo necessário armazenar um novo dado na cache e não havendo espaço disponível, pois todas as posições estão ocupadas, devem-se remover determinados elementos para liberar espaço. A forma utilizada para selecionar o elemento a ser retirado é comandada por uma política de troca (replacement policy). Uma das políticas de troca mais utilizada é a LRU (least recently used), que remove o elemento recentemente menos usado.

Armazenamento de informações da Cache

Quando um dado é armazenado na cache, como resultado de um processamento realizado pelo processador, em algum momento ele deve ser gravado de volta no local de armazenamento original.

|

||||

|

É função da política de escrita (write policy) determinar o momento em que ocorrerá a gravação dos dados da cache em seu local original. Para isso, existem os seguintes tipos:

- Política write-through (escrita através): cada vez que um elemento é escrito na cache, ele também é gravado no local de armazenamento original. Assim, a memória que está hierarquicamente abaixo possuirá a informação atualizada, facilitando a remoção do conteúdo da cache. Por outro lado, cada operação na cache resulta uma operação na memória, o que torna o acesso mais lento.

- Política write-back (escrever de volta): as escritas são realizadas apenas na cache. Quando a informação for ser removida, são identificados quais dos elementos foram alterados e somente essas posições são escritas de volta nos locais de armazenamento originais. Com isso, é reduzido o tempo que se leva para escrever na memória, pois é reduzida a quantidade de operações de escrita na memória. No entanto, quando um dado que deve ser removido (para liberar espaço para outro) foi modificado, é necessário que o novo conteúdo aguarde o conteúdo a ser removido ser escrito no outro nível da hierarquia. Outro problema é que nem sempre existirá consistência entre os dados que estão na cache e na memória.

|

||||

|

Organização de cache

A cache pode ser organizada de duas formas: separando dados das instruções ou unificada.

Na cache separada, são utilizados locais distintos para armazenar os dados e as instruções, permitindo que o processador acesse simultaneamente instruções (na cache de instruções) e dados (na cache de dados). Como geralmente as instruções dos programas não são alteradas, estas informações podem ser facilmente descartadas e como instruções ocupam menos espaço, é possível destinar mais espaço para armazenamento de dados.

Já na cache unificada é utilizado o mesmo espaço de armazenamento tanto para instruções quanto para dados.

Cache de processador

Como forma de minimizar a diferença de velocidade entre processador e memória RAM passou a ser usada a memória cache, baseada na memória SRAM. Trata-se de uma memória de acesso rápido, servindo para armazenar os dados mais frequentemente usados pelo processador.

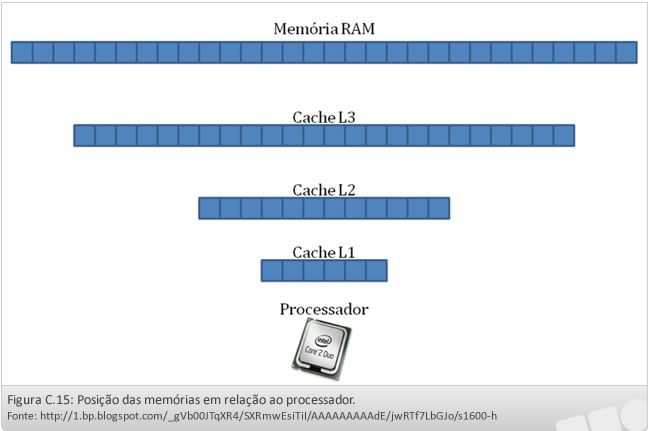

O seu objetivo é o de evitar, na maioria das vezes, que o processador tenha que acessar a memória principal, que, comparativamente, é mais lenta. Atualmente os sistemas utilizam mais de um nível de cache na hierarquia de memória, sendo a cache primária, ou cache L1 (level 1), cache L2 (level 2) e cache L3 (level 3).

A cache L1 fica próxima ao núcleo do processador e o acompanha em velocidade, apresentando tempos de latência extremamente baixos. Ela é organizada separando a área de instruções da área de dados.

As demais caches são organizadas de forma unificada, sendo que cada nível hierarquicamente inferior (L2, L3) apresenta maior capacidade de armazenamento, porém maior distância do processador, resultando em tempos de acesso superior em relação às que se encontram nos níveis superiores.

A leitura de dados no processador começa sempre no cache L1, caso o dado seja encontrado, o processador não perderá tempo. Caso o dado não esteja no cache L1, o próximo a ser acessado será o cache L2, encontrando o que procura nele, o processador já perderá algum tempo, mas não tanto quanto na RAM, e assim sucessivamente. Caso os dados não estejam em nenhum dos níveis de cache, a memória RAM deverá ser acessada, resultando em um processo mais lento. Quando o processador precisa ler dados na memória principal, o controlador de cache transfere blocos de dados da RAM para a cache do nível mais baixo até a cache L1 que será acessada pelo processador. Conforme segue:

Referente ao tempo de acesso, para efeitos de comparação, temos os seguintes valores:

- Cache L1: cerca de 3 a 4 ciclos

- Cache L2: cerca de 10 a 15 ciclos

- Memória RAM: cerca de 140 ciclos

Função da cache de processador

A cachê, anteriormente, era limitada a armazenar cópias das últimas informações acessadas pelo processador, descartando as informações mais antigas ou menos acessadas trabalhando de forma unificada.

Atualmente, a cache, como visto anteriormente, pode trabalhar de forma unificada ou separando instruções de dados. Ela também conta com sistema de prefetch, que monitora o fluxo de instruções, carregando antecipadamente dados que poderão ser necessários nos ciclos seguintes.

Ela acelera a operação de escrita, pois o processador grava diretamente nela e o controlador de cache fica encarregado de gravar os dados na memória RAM posteriormente.

A cache L1 passou a ser dividida em dois blocos independentes, sendo um destinado para o armazenamento de dados e outro para o de instruções, o que possibilita que o processador leia dados e instruções simultaneamente.

A cache exerce contato direto com a memória principal, seja gravando ou lendo informações. Para agilizar essa relação existe um elemento chamado TLB (Translation lookaside buffer), que fica localizado entre a cache L2 (ou L3, se for o caso) e a memória RAM. Ele armazena os endereços de memória, convertendo os endereços lógicos (que são usados por aplicativos em execução) em endereços físicos presentes na memória principal. Isso é necessário, pois no momento da execução de um processo, ele referencia endereços virtuais, com os quais eles trabalham, mas que devem ser traduzidos para endereços reais, que podem ser acessados pelo processador.